Seite 1 von 2

2x IP-Stack von Harrison Pham

Verfasst: Fr 17. Jan 2014, 11:20

von PIC18F2550

Hi,

kann ich mit dem IP-Stack von Harrison Pham auch 2 ENC28j60 betreiben oder kommen da irgendwelche Softwareteile aneinander?

Die Steuer und datenleitungen zum ENC sind sepperat.

Im Spinncode werde ich dann die Variabeln/Konstanten doppeln müssen.

Re: 2x IP-Stack von Harrison Pham

Verfasst: Fr 17. Jan 2014, 19:21

von joergd

Es geht sicher mit 2x driver_enc28j60 ("Hardware-Treiber") und 2x driver_socket (TCP-Stack), besonders schön ist das dann aber nicht. Schöner wäre 2x driver_enc28j60 und 1x driver_socket. Da müßte man aber wohl Einiges an driver_socket schrauben. Und auch driver_enc28j60 könnte man sicher noch so ändern, daß er 2 ENC28j60 bedienen kann.

Darf man fragen, was Du damit machen willst? Einen Router bauen?

Re: 2x IP-Stack von Harrison Pham

Verfasst: Sa 18. Jan 2014, 00:49

von PIC18F2550

Hi joergd,

alles nur options suche. Router/Firewall/Server.... ist auch dabei.

Habe noch ein bisschen Platz auf ner platte und überlege was ich da alles noch rein Packen könnte.

Re: 2x IP-Stack von Harrison Pham

Verfasst: Sa 18. Jan 2014, 13:19

von Micha

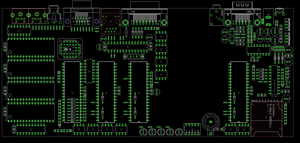

Was machst du denn hier für tolle Sachen PIC? - das Layout erinnert irgendwie stark an einen Hive mit zusätzlichem Kram auf der Platine - bin schon gespannt ob du uns in Garitz mit nem "Super Hive" der zweiten Generation überraschst

Re: 2x IP-Stack von Harrison Pham

Verfasst: Sa 18. Jan 2014, 23:20

von PIC18F2550

Super Hive

nee nur auf dem 1. Blick dazu sind die unterschiede zu groß.

-

2Mb linear adressierbarer sram

-

512k Boot Flasch mit System Programmen

-

externer Funktionsdekoder SRAM/FLASH/LATCH/CS(von den Prop-chips)

-

9 Bit Datenbus

-

6,25Mhz Systemtakt aus ENC28J60 oder extra Quarzoszillator 5Mhz

-

Tokenring über alle Chips Teilnehmer über DIP-Schalter zu/abschaltbar

-

Serielle schnittstelle einstellbar auf DTE/DCE oder Programmierung ohne Hardware-Handshake

-

Externes 5V 2A Netzteil

-

2x 3,3V Stepdown Regler 1x soll für SD-Karte sein.

-

Rückopplungsfreie Busanpassung 5V/3,3V

-

Stereowiedergabe mit 2 12Bit D/A Wandler

-

Stereoaufnahme mit 2x 12 Bit A/D Wandler Ue 1Vss

-

Joystik/Joypad anschluß analog / digital

-

Modbus RTU aktiv/passiv, Master/Slave an stelle von Tokenring Teilnehmer DIP-Schalter zu/abschaltbar

Re: 2x IP-Stack von Harrison Pham

Verfasst: Mo 20. Jan 2014, 10:53

von yeti

PIC18F2550 hat geschrieben:- 25Mhz Systemquarz

Rennt dann die PLL nicht zu schnell?

Wenn Du eh ENC28J60er einplanst, kannste von denen 6,25MHz bekommen...

Re: 2x IP-Stack von Harrison Pham

Verfasst: Mo 20. Jan 2014, 13:51

von PIC18F2550

PIC18F2550 hat geschrieben:Rennt dann die PLL nicht zu schnell?

Ja mit 100Mhz.

Bei mir laufen 4 Stück mit 100Mhz seit ca. 6Monaten ohne Probleme durch.

Thermisch kein unterschied zu 80Mhz.

die 4 Props schieben einfach seriell Daten über eine Ringleitung.

Intern werden alle 8 COGs auch mit dem Datentransfer beauftragt.

Der 1. PROP sendet ein Zufallsmuster und prüft am ende ob alles fehlerfrei ist ansonsten gibt er eine Fehlermeldung ab.

Ein Prop habe ich mit (4x32Mhz) 128Mhz getestet das macht er auch noch mit wird aber schon warm.

PIC18F2550 hat geschrieben:Wenn Du eh ENC28J60er einplanst, kannste von denen 6,25MHz bekommen...

Bild/Plan? Danke gern

Re: 2x IP-Stack von Harrison Pham

Verfasst: Mo 20. Jan 2014, 14:47

von yeti

http://ww1.microchip.com/downloads/en/D ... 39662a.pdf ... Pin 3 des Chips (beim 28-Pin-SPDIP, SSOP-, -SOIC-Gehäuse) ist der Taktausgang.

Die SPI-Routinen für den ENC28J60 müssen dann nochmal kritisch beäugt werden, ob sie den Chip bei 80 MHz bereits ausreizen. Das schüttel ich grad nicht mehr auswendig aus meinem Bioassoziator...

----------

Edit 20140122:

http://ww1.microchip.com/downloads/en/D ... 39662c.pdf ist insgesamt korrekter.

Da die Prerelease des Datenblattes bezüglich Pinout ok war, dachte ich erst man könne sie gefahrlos hier als Quelle angeben, aber das führt zu Wervirrung bezüglich anderer Behauptungen in der Vorabversion, die später revidiert wurden...

Hit shappens!

Re: 2x IP-Stack von Harrison Pham

Verfasst: Mo 20. Jan 2014, 15:51

von PIC18F2550

Da hängen gut 10cm leiterbahn drann und dann 4 Eingänge.

Das könnte kapazitiv durchaus schon Auswirkung auf die Stabilität haben da nur 8mA zulässig sind.

Ansonnsten müsste ich mit einem Gatter(aus dem GAL16V8) nachhelfen. Mal sehen wie sich das macht.

Re: 2x IP-Stack von Harrison Pham

Verfasst: Di 21. Jan 2014, 23:49

von PIC18F2550

@yeti:

Die zentrale Taktspeisung funktioniert auch mit 6x Propeller meine Zweifel waren also zu Unrecht und deine Idee ist super.

Die SPI-Routienen waren doch auch bei der Hydra am werkeln die lief doch mit 100Mhz denke ich jedenfals.

Irgendwie geht mir der Gedanke ein Modbus an das System zu knüpfen nicht aus dem Sinn

Platz gibt es noch reichlich.

- Noch genug Platz!!